- 您现在的位置:买卖IC网 > Sheet目录1249 > TS-MAC-XM-UT4 (Lattice Semiconductor Corporation)SITE LICENSE ETH MAC TRI-SPD XP

�� �

�

Lattice� Semiconductor�

�Support� Resources�

�?� TN1196� -� LatticeECP3� Marvell� 1� GbE� (1000BASE-X)� Physical/MAC� Layer� Interoperability�

�?� TN1197� -� LatticeECP3/Marvell� SGMII� Physical/MAC� Layer� Interoperability�

�LatticeSCM�

�?� DS1004� ,� LatticeSC/M� Family� Data� Sheet�

�?� DS1005� ,� Lattice� SC/M� Family� flexiPCS� Data� Sheet�

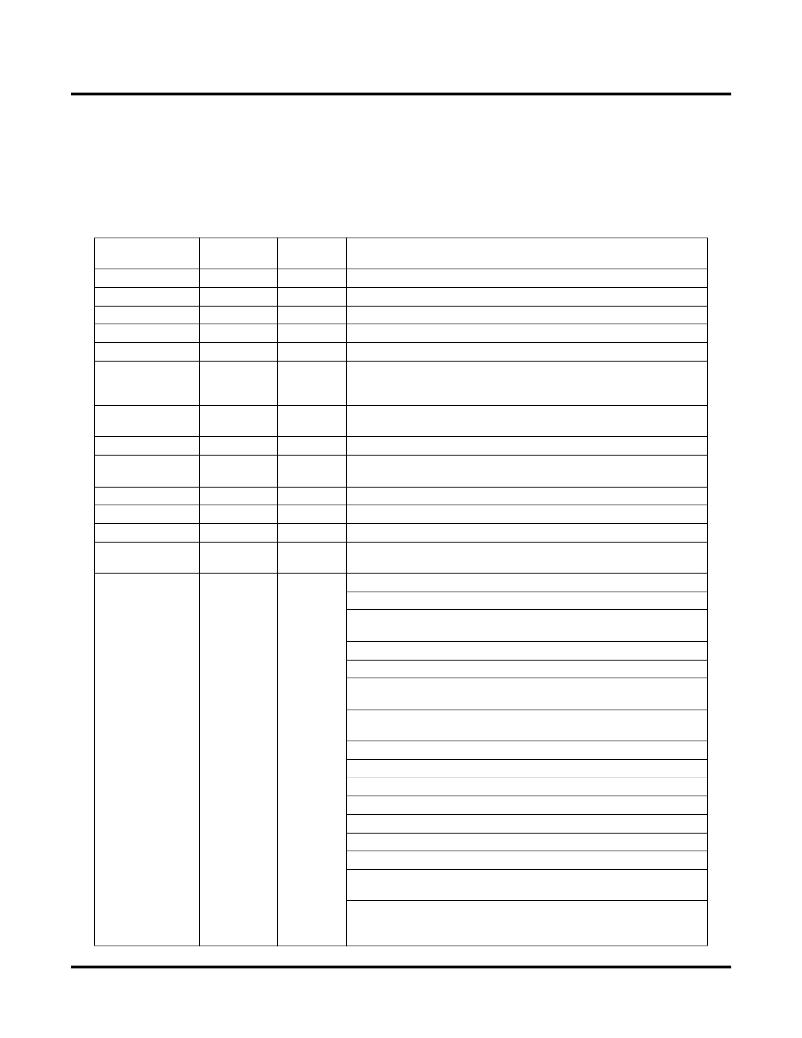

�Document�

�IP� Core�

�Date�

�February� 2006�

�May� 2006�

�July� 2006�

�November� 2006�

�May� 2007�

�August� 2007�

�Version�

�01.0�

�01.1�

�01.2�

�01.3�

�01.4�

�01.5�

�Version�

�2.0�

�2.1�

�2.2�

�2.3�

�2.4�

�2.4�

�Change� Summary�

�Initial� release.�

�Added� support� for� LatticeECP2� family.�

�Added� support� for� LatticeSC� family.�

�Added� support� for� LatticeECP2M� family.�

�Added� support� for� LatticeXP2� family.�

�Revised� Transmit� and� Receive� Control� Register� Description.�

�Updated� description� and� diagram� for� Successful� Transmission� of� a�

�64-Byte� Frame� -Tx� MAC� Application� Interface.�

�September� 2007�

�01.6�

�2.4�

�Updated� description� for� Bit� 30� in� the� Receive� Statistics� Vector�

�Description� table.�

�September� 2007�

�November� 2007�

�01.7�

�01.8�

�2.4�

�2.4�

�Updated� MAC� Address� Register� mnemonic� and� POR.�

�Updated� Performance� and� Resource� Utilization� table� in� the�

�LatticeXP2� appendix.�

�January� 2008�

�January� 2008�

�January� 2008�

�June� 2008�

�01.9�

�02.0�

�02.1�

�02.2�

�2.5�

�2.5�

�2.5�

�2.6�

�Added� Software� Requirements� text� section.�

�Updated� the� Core� Generation� and� Simulation� section.�

�Updated� part� numbers� listed� in� appendices.� U2� changed� to� U3.�

�TSMAC� IP� core� Internal� Registers� table� -� Corrected� the� POR� value�

�for� Inter-Packet� Gap� Register.� Value� changed� to� 000CH.�

�September� 2008�

�02.4�

�2.7�

�Expanded� Feature� list.�

�Updated� General� Description� text� section.�

�Added� Tri-Speed� 10/100/1G� Ethernet� MAC� Core� Block� Diagram�

�(Gigabit� MAC� or� SGMII� Easy� Connect� options).�

�Added� VLAN-Tagged� Ethernet� Frame� Format� diagram.�

�Added� Ethernet� Control� Pause� Frame� Format� diagram.�

�Added� Tri-Speed� 10/100/1G� Ethernet� MAC� Core� System� Block� Dia-�

�gram� (Gigabit� MAC� option).�

�Added� Tri-Speed� 10/100/1G� Ethernet� MAC� Core� System� Block� Dia-�

�gram� (SGMII� Easy� Connect� option).�

�Updated� Signal� Descriptions� table.�

�Updated� Parameter� Descriptions� table.�

�Updated� Receiving� a� PAUSE� Frame� text� section.�

�Updated� Receive� Statistics� Vector� Description� table.�

�Updated� Internal� Data� Buffer� and� FIFO� Interfaces� text� section.�

�Updated� Internal� Registers� text� section.�

�Updated� MODE� (R/W)� Register� Descriptions� table.�

�Updated� Transmit� and� Receive� Control� (R/W)� Register� Descriptions�

�table.�

�Added� the� Core� Generation� text� section.�

�IPUG51_03.0,� December� 2010�

�61�

�Tri-Speed� Ethernet� MAC� User’s� Guide�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

TS250-130F-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-B-0.5-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-RB-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-RC-2

POLYSWITCH PTC RESET 0.13A SMD

TS250-130F-RC-B-0.5-2

POLYSWITCH PTC RESET 0.13A SMD

TS600-170F-2

POLYSWITCH PTC RESET 0.17A T/R

TS600-200F-RA-B-0.5-2

POLYSWITCH PTC RESET 0.20A SMD

TS600-400F-2

POLYSWITCH PTC RESET 0.40A SMD

相关代理商/技术参数

TSMBG0505C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|100V V(BO) MAX|DO-215AA

TSMBG0506C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|110V V(BO) MAX|DO-214AA

TSMBG0507C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|145V V(BO) MAX|DO-214AA

TSMBG0509C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|185V V(BO) MAX|DO-215AA

TSMBG0510C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|200V V(BO) MAX|DO-214AA

TSMBG0511C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|210V V(BO) MAX|DO-214AA

TSMBG0512C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|215V V(BO) MAX|DO-214AA

TSMBG0514C

制造商:未知厂家 制造商全称:未知厂家 功能描述:SINGLE BIDIRECTIONAL BREAKOVER DIODE|250V V(BO) MAX|DO-214AA